CPLDs

More from the Category

In the ever-evolving landscape of digital electronics, programmable logic devices (PLDs) have emerged as indispensable tools for implementing intricate logic functions and digital circuits. Among these versatile devices, Complex Programmable Logic Devices (CPLDs) stand out, providing a flexible and powerful solution for designing and prototyping digital systems.

What is a CPLD?

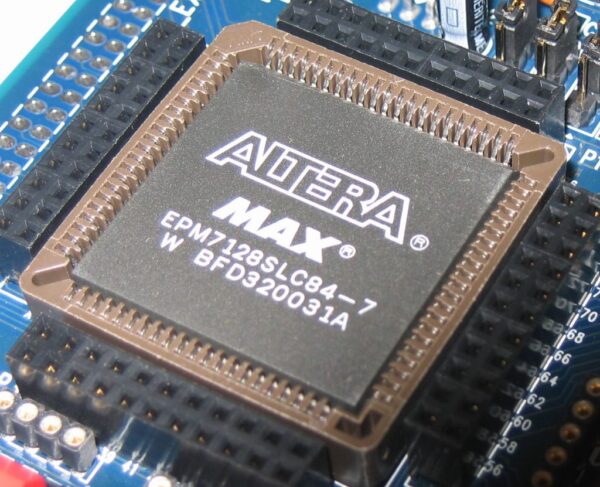

Complex Programmable Logic Devices (CPLDs) are integrated circuits that belong to the family of programmable logic devices. They contain a matrix of programmable logic blocks interconnected through programmable interconnects, thus offering a flexible solution for implementing complex digital circuits. CPLDs have evolved from Simple PLDs (SPLDs) and provide more significant capacity and enhanced functionality.

CPLD Architecture

At the core of a CPLD lies an array of programmable logic cells or macrocells. Each microcell is capable of implementing a small logic function, typically a 2-to-1 multiplexer or D flip-flop. These macrocells are programmable and can be interconnected to form the desired digital logic circuit. The interconnects provide the flexibility to route signals between marcocells, enabling the implementation of complex and customized logic functions.

Benefits of CPLDs

CPLDs offer several advantages that make them attractive for various applications:

Flexibility

CPLDs offer a high degree of flexibility, allowing designers to implement a wide range of custom logic functions. Unlike fixed function logic gates or ASICs (Application-Specific Integrated Circuits), CPLDs can be programmed and reprogrammed to suit changing design requirements. This flexibility makes CPLDs ideal for prototyping and designing digital systems where the functionality may evolve during the development process. Designers can quickly modify the logic implemented in the CPLD to adapt to new specifications or design changes without the need for costly hardware redesigns.

Low Power Consumption

Compared to other programmable logic devices like FPGAs, CPLDs typically consume lower power. This characteristic makes them well-suited for power-constrained applications where minimizing power consumption is critical. By efficiently implementing specific logic functions in a CPLD, designers can achieve a balance between performance and power consumption, making these devices ideal for battery-powered and portable electronic devices.

Fast Development Time

CPLDs significantly reduce the development time of digital systems compared to custom ASICs. Developing an ASIC involves a lengthy and expensive fabrication process, which includes designing and manufacturing the silicon chip. In contrast, CPLDs are the-shelf devices that can be programmed with the desired logic in a matter of minutes for rapid prototyping and iterative design. This faster development cycle allows for rapid prototyping and iterative design improvements, saving time and resources during the product development phase.

High Reliability

CPLDs offer high reliability in electronic systems. Since CPLDs are typically implemented on Field-Programmable Gate Arrays (FPGAs), they benefit from the inherent reliability and robustness of FPGA technology. Additionally, the programmable nature of CPLDs allows for thorough testing and verification before deployment, reducing the likelihood of errors or defects. Their resistance to physical damage, such as vibrations or shocks, contributes to the overall reliability and longevity of the electronic systems in which they are used.

Cost

CPLDs are generally more cost-effective than ASICs, especially for low to mid-volume production. Developing custom ASICs involves substantial upfront costs for design, fabrication, and testing. On the other hand, CPLDs are commercially available and do not require the significant initial investment associated with ASIC development. This makes CPLDs an attractive option for projects with moderate production volumes, as it reduces the overall development and production costs.

Easy Prototyping and Iterative Design

CPLDs allow designers to prototype and experiment with different logic configurations quickly. This ease of prototyping facilitates rapid iteration and testing of designs, enabling engineers to explore multiple design possibilities before settling on the final implementation. It encourages an agile development approach and supports faster time-to-market for new products or system enhancements.

Applications of CPLDs

CPLDs find applications across various industries and sectors, including:

Communications

In the communications industry, CPLDs are widely used in network equipment and infrastructure. They play a crucial role in managing data flow, packet routing, and protocol handling. These devices can efficiently handle various communication standards and interfaces, making them ideal for applications such as routers, switches, modems, and network interface cards. CPLDs help in managing data traffic, optimizing data paths, and enabling smooth communication between different network components.

Consumer Electronics

CPLDs are employed in consumer electronics to control and manage various functions. In devices like smart TVs, CPLDs handle interface management for display panels and audio processing. They can also be used in set-top boxes, home automation systems, gaming consoles, and multimedia devices to handle input/output operations, interface with different peripherals, and manage device-specific functionalities efficiently.

Automotive

In the automotive industry, CPLDs are utilized in various critical applications. They can be found in engine control units (ECUs) to control fuel injection timing and other engine-related functions. CPLDs are also used in safety systems, such as airbag deployment and antilock braking systems (ABS). Additionally, advanced driver assistance systems (ADAS) rely on CPLDs for tasks like processing sensor data, implementing decision-making algorithms, and controlling actuators for features like adaptive cruise control and lane departure warning systems.

Industrial Automation

CPLDs are an integral part of industrial automation systems. They are used in Programmable Logic Controllers (PLCs) to control and monitor industrial processes. CPLDs in PLCs enable the implementation of custom logic, safety interlocks, and communication interface to interact with various sensors, data processing, and actuator interfacing, allowing precise and efficient automation of industrial tasks.

Aerospace and Defense

In aerospace and defense systems, CPLDs are deployed in critical and safety-critical systems. They are used in avionics for tasks like radar signal processing, flight control systems, and navigation. CPLDs also play a role in secure communications and encryption, ensuring the protection of sensitive data in defense applications. Their ability to handle custom logic makes them valuable components in aerospace and defense systems, where performance, reliability, and security are paramount.

Design Flow for CPLDs

The design flow for CPLDs involves several essential steps:

Requirements Analysis

In this initial stage, the design team collaborates with stakeholders to clearly define the project requirements and specifications. They gather information on the desired functionality of the CPLD, including input and output requirements, timing constraints, power constraints, and any other critical performance goals. Understanding the system-level requirements is crucial to ensure that the CPLD implementation meets the intended objectives. This phase also involves identifying potential challenges or limitations that might influence the design choices.

Design Entry

With a clear understanding of the requirements, the design entry phase involves creating a hardware description of the logic circuit using a Hardware Description Language (HDL) such as VHDL (VHSIC Hardware Description Language) or Verilog. HDLs allow designers to express the behavior and structure of digital systems t a high level, abstracting away the underlying hardware details. Designers use HDL to define the functionality and interconnections of the logic blocks within the CPLD.

Synthesis

Once the design is captured in an HDL, the next step is synthesis. Synthesis is the process of converting the high-level HDL code into a low-level representation called a netlist. The netlist is a hierarchical representation of the design, capturing the logical structure of the circuit in terms of gates, flip-flops, and other fundamental logic elements available in the target CPLS. Synthesis tools analyze the HDL code and perform optimizations to generate an efficient netlist that meets that performance and resource requirements.

Implementation

In this phase, the synthesized netlist is mapped onto the actual architecture of the target CPLD. The CPLD vendor provides specific tools that handle the implementation process. During implementation, the tools that handle the implementation process. During implementation, the tools place the logic cells, macros, and other components on the physical resources of the CPLD device. The tools also handle the routing of interconnections, ensuring that the design’s logical connections are appropriately established on the physical device. The goal is to achieve the best possible mapping and outing to meet the timing and performance constraints.

Verification

Before moving forward, designers must thoroughly test and validate the functionality of the design. This is typically done using simulation tools, where test benches and stimuli are created to exercise the design under various scenarios and edge cases. Simulation allows designers to catch and fix any potential bugs, functional issues, or timing violations before proceeding to the physical implementation. Verification is an iterative process, and designers may need to refine their design and simulation tests to ensure correctness and robustness.

Programming

After the design is successfully verified, the final step is to program the CPLD with the generated configuration bitstream. The configuration bitstream contains the information necessary to configure the CPLD’s internal connections and resources to implement the desired logic circuit. The bitstream is generated by the implementation tools and is specific to the target CPLD device. Programming can be done using dedicated hardware programmers or, in some cause, by the system microcontroller or processor if the CPLD is part of a larger system.

Tips for Working with CPLDs

Modular Design

Adopting a modular approach is a fundamental strategy when working with CPLDs. Breaking down the overall design into smaller, manageable modules offers several advantages. Firstly, it simplifies the development process, allowing multiple team members to work on different modules concurrently. This parallel development can significantly reduce the overall design time. Additionally, a modular design promotes easier debugging, as individual modules can be tested and verified independently. Moreover, modular designs facilitate design reuse, enabling you to apply proven modules in future projects, further streamlining your development workflow.

Resource Utilization

Effectively utilizing the available resources of the CPLD is crucial for maximizing its potential. CPLDs come with a finite number of logic cells and interconnects, so optimizing their use becomes essential, especially when dealing with complex designs. Avoiding unnecessary logic duplication, sharing resources between modules, and employing efficient coding techniques can help save valuable resources and potentially allow for the implementation of more extensive and sophisticated functionalities within the same device.

Comprehensive Test Benches

Rigorous testing and verification are critical steps in ensuring the correctness and reliability of your CPLD design. Creating comprehensive test benches that encompass various test cases and scenarios can significantly reduce the risk of errors and uncover potential issues early in the design process. By thoroughly validating the design in simulation, you can have confidence in its functionality before committing to programming the CPLD, thus saving time and avoiding costly rework.

Vendor Tools

Familiarity with the CPLD vendor’s design software is invaluable for efficient development. Each vendor typically provides specialized software tools to support the design, synthesis, verification, and programming of their CPLD devices. Investing time in mastering these tools can offer benefits such as better optimization, improved debugging capabilities, and access to vendor-specific IP cores or libraries. Stay updated with the latest tool releases to leverage any new features or improvements that may enhance your design flow.

Apply Timing Constraints

In digital circuits, timing is crucial to ensure proper operation and meet performance specifications. Applying timing constraints to your CPLD design helps enforce setup and hold times for flip-flops and combinatorial paths. This practice ensures that signals reach their destinations within the required clock cycles, preventing timing violations that could lead to faulty operation or decreased performance. By properly managing timing, you can enhance the reliability and predictability of your CPLD-based system.

Design Reuse

Leveraging existing Intellectual Property (IP) cores and design libraries can significantly expedite the development process and save valuable design time. Many CPLD vendors offer pre-designed and verified IP cores that you can integrate into your projects. These IP cores cover common functions like memory controllers, communication protocols, or arithmetic units, allowing you to focus on the unique aspects of your design. By reusing proven and optimized IP, you not only accelerate your development but also benefit from the reliability and performance of established modules.

Looking Ahead

Complex Programmable Logic Devices (CPLDs) have proven to be a valuable asset in the world of digital electronics, enabling engineers to implement complex logic functions with ease and flexibility. With their numerous benefits, wide-ranging applications, applications, and streamed design flow, CPLDs continue to be a preferred choice for many digital designers. As technology advances, CPLDs are likely to keep evolving, offering even more power and efficiency for the implementation of cutting-edge digital systems.

Their compact size and inherent re-programmability of CPLDs make them an attractive option for space-constrained applications and rapid design iterations. This dynamic nature allows engineers to make iterative changes without incurring the costs and delays associated with traditional ASICs, fostering a quicker time-to-market for innovative products. As CPLD technology advances and their capabilities expand, they are bound to play a pivotal role in shaping the future of digital electronics, unlocking even greater possibilities for advanced digital system designs across diverse industries and applications.

Partner with Microchip USA

To explore how CPLDs can enhance your next design, partner with Microchip USA for a reliable supply of top-quality CPLDs and expert support. Contact us today!